## **University of Huddersfield Repository**

Dafinoiu, A.A.

Investigation of heterogeneous computing through novel parallel programming platforms

#### **Original Citation**

Dafinoiu, A.A. (2016) Investigation of heterogeneous computing through novel parallel programming platforms. Masters thesis, University of Huddersfield.

This version is available at http://eprints.hud.ac.uk/id/eprint/31698/

The University Repository is a digital collection of the research output of the University, available on Open Access. Copyright and Moral Rights for the items on this site are retained by the individual author and/or other copyright owners. Users may access full items free of charge; copies of full text items generally can be reproduced, displayed or performed and given to third parties in any format or medium for personal research or study, educational or not-for-profit purposes without prior permission or charge, provided:

- The authors, title and full bibliographic details is credited in any copy;

- A hyperlink and/or URL is included for the original metadata page; and

- The content is not changed in any way.

For more information, including our policy and submission procedure, please contact the Repository Team at: E.mailbox@hud.ac.uk.

http://eprints.hud.ac.uk/

## INVESTIGATION OF HETEROGENEOUS COMPUTING THROUGH NOVEL PARALLEL PROGRAMMING PLATFORMS

## ANDREI-ALEXANDRU DAFINOIU

A thesis submitted to the University of Huddersfield in partial fulfilment of the requirements for the degree of Masters of Science by Research

Supervised by Dr. Violeta Holmes

The University of Huddersfield

September 2016

#### Abstract

The computational landscape is dominated by the use of a very high number of CPU resources; this has however provided diminishing returns in recent years, pushing for a paradigm shift in the choice for computational systems.

The following work was aimed at determining the maturity of heterogeneous computer systems in terms of computational performance and their possible integration within High-Performance Computing resources through the use of the OpenCL parallel programming platform.

An introduction is given in the existing hardware architectures targeted by the OpenCL platform, existing literature regarding the integration of heterogeneous systems for computational applications, and the OpenCL platform as a development environment.

A number of applications are developed to benchmark the capabilities of the framework in multi-architecture environments, the results of which show up to 160 times performance gain when targeting GPU architectures, as opposed to CPU, for matrix multiplication algorithms.

Based on this, an extensive test-bench is designed targeting the HTCondor resource pool for a Fast-Fourier Transform application. Results from these machines once again showed a significant performance increase against CPU systems, while also enabling the expansion of the HTCondor system and the uncovering of 30 Teraflops of dormant computing power.

The FPGA architecture is also investigated for its potential in OpenCL computational acceleration, with a focus on the platforms ease of use. It is determined that the framework is mature enough for FPGA application development.

## Acknowledgements

I would like to express my thanks to Dr. Violeta Holmes, and the High-Performance Computing Research Group for their wisdom, support, and friendship. Their input has been invaluable to me during my time at the University of Huddersfield, and without them this work would have not been completed on time.

## **Table of Contents**

| Chapter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| <ul> <li>1.1 Heterogeneous Computing</li> <li>1.2 The OpenCL heterogeneous framework</li> <li>1.3 Reconfigurable Computing</li> <li>1.4 Methodology</li> <li>1.5 Research Questions:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 | 12<br>13<br>17                             |

| Chapter 2: Literature Review                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20                                         |

| <ul> <li>2.1 Many-Core Architectures</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21<br>22                                   |

| <ul> <li>2.4.1 Radar Processing: FPGAs or GPUs?</li> <li>2.4.2 A Comparison Study on Implementing Optical Flow and Digital Communication<br/>FPGAs and GPUs</li> <li>2.4.3 Performance Comparison of GPU, DSP and FPGA implementations of in<br/>processing and computer vision algorithms in embedded systems</li> <li>2.4.4 Accelerating High-Performance Computing With FPGAs.</li> <li>2.4.5 OpenCL: A Parallel Programming Standard for Heterogeneous Computing System</li> <li>2.4.6 A Comprehensive Performance Comparison of CUDA and OpenCL</li> </ul> | ons on<br>24<br>image<br>25<br>26<br>ms 28 |

| 2.5 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                         |

| Chapter 3: The OpenCL Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31                                         |

| 3.1 Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                                         |

| <ul> <li>3.1.1 Environment Setup.</li> <li>3.1.2 Host Initialization.</li> <li>3.1.3 Kernel Setup.</li> <li>3.1.4 Execution .</li> <li>3.1.5 Clean-up.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               | 34<br>35<br>36                             |

| 3.2 On-going Improvements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37                                         |

| <ul><li>3.2.1 Shared Virtual Memory</li><li>3.2.2 Device Kernel Enqueue</li><li>3.2.3 Standard Portable Intermediate Representation (SPIR-V)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                          | 38                                         |

| 3.3 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40                                         |

| Chapter 4: OpenCL Multi-Architecture Application Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41                                         |

| <ul><li>4.1 OpenCL System Detection</li><li>4.2 Application Design</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |

| 4.2.1 Host Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44                                         |

| 4.2.2 Kernel Code                                        | 49 |

|----------------------------------------------------------|----|

| 4.3 Test Bench Environment                               |    |

| 4.3.1 System Specifications                              |    |

| • •                                                      |    |

| 4.4 Application Execution                                |    |

| 4.4.1 System I                                           |    |

| 4.4.2 System II                                          |    |

| 4.4.3 System III<br>4.4.4 System IV                      |    |

| -                                                        |    |

| 4.5 Conclusions                                          |    |

| Chapter 5: OpenCL framework implementation over HTCondor |    |

| 5.1 Fast Fourier Transforms                              |    |

| 5.2 Benchmark Execution                                  |    |

| 5.3 HTCondor Related Scripts                             |    |

| 5.3.1 Condor Individual Unit Execution                   |    |

| 5.3.2 Individual Machine Benchmarking                    |    |

| 5.3.3 Data sorting and processing                        |    |

| Chapter 6: OpenCL FPGA Acceleration                      |    |

| 6.1 Hardware Description Language                        |    |

| 6.2 Altera SDK for OpenCL                                |    |

| 6.2.1 Altera Offline Compiler                            |    |

| 6.2.2 Application porting                                |    |

| 6.3 DE1 System-on-Chip                                   |    |

| 6.3.1 Setup                                              |    |

| 6.4 Benchmark Application                                |    |

| 6.5 Execution                                            |    |

| 6.6 Conclusion                                           |    |

| Chapter 7: Further Research                              |    |

| Chapter 8: Summary and Conclusions                       |    |

| Chapter 9: References                                    |    |

| Chapter 10: Appendix                                     |    |

Final Word Count: 17,945

## List of Figures

| Figure 1: CPU Frequency Evolution (GHz)                   | 9    |

|-----------------------------------------------------------|------|

| Figure 2: Intel CPU Architecture Size Evolution (Intel)   | . 10 |

| Figure 3: Host and Various Accelerators (CMSoft)          | . 12 |

| Figure 4: FPGA Basic Outline (Mazsola)                    |      |

| Figure 5: C to RTL Converter Using HLS (Aldec)            | . 16 |

| Figure 6: Many-Core Processor architecture (Embedded.com) |      |

| Figure 7: CPU - GPU Core Count                            |      |

| Figure 8: OpenCL Programming Flow                         | . 33 |

| Figure 9: Excerpt of Device Detection Application         |      |

| Figure 10: Device Report for Development PC               | . 43 |

| Figure 11: Memory Buffer Allocation                       | . 44 |

| Figure 12: Function for Matrix Element Allocation         | . 45 |

| Figure 13: Identifying Available Platforms.               |      |

| Figure 14: Device Cycle Loop                              |      |

| Figure 15: CPU/GPU Decision Point                         | . 46 |

| Figure 16: Command Queue Initialization                   | . 47 |

| Figure 17: Building Program Executable                    |      |

| Figure 18: Allocating Device Memory                       |      |

| Figure 19: Kernel Argument Passing                        | . 48 |

| Figure 20: Command Enqueue                                |      |

| Figure 21: Data Retrieval and Profiling                   |      |

| Figure 22: Memory Clearing                                | . 49 |

| Figure 23: OpenCL Kernel Code                             | . 50 |

| Figure 24: External Argument Code Snippet                 |      |

| Figure 25: CPU Matrix Multiplication                      |      |

| Figure 26: GPU Matrix Multiplication                      | . 54 |

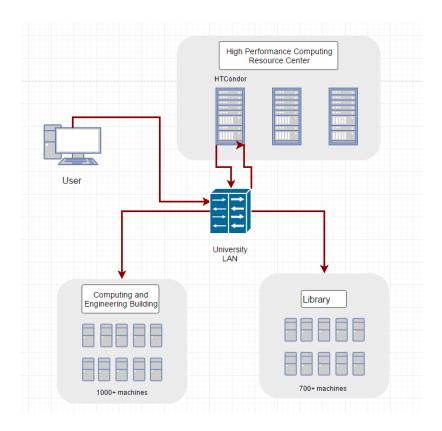

| Figure 27: Condensed Path of HTCondor Access              | . 65 |

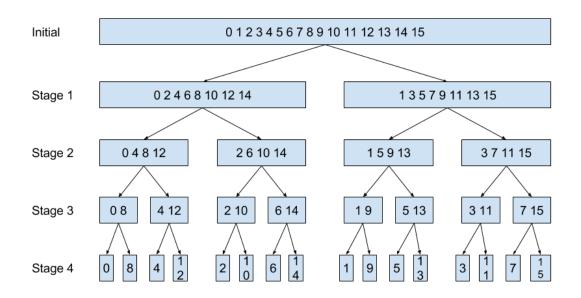

| Figure 28: FFT Interlaced Decomposition                   | . 68 |

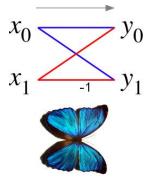

| Figure 29: FFT Butterfly Calculation                      | . 69 |

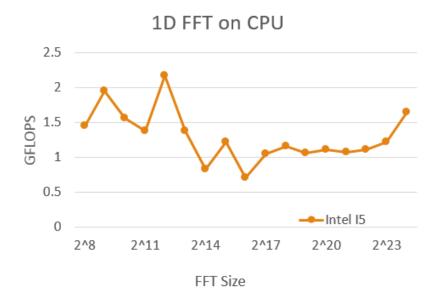

| Figure 30: CPU Benchmark                                  |      |

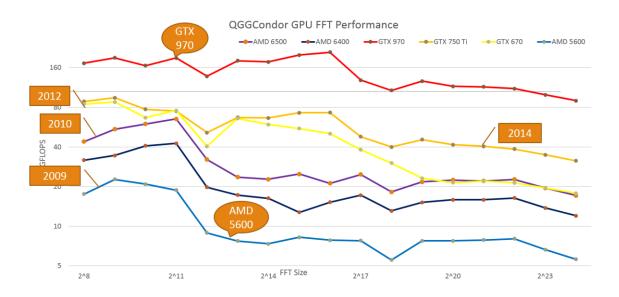

| Figure 31: GPU FFT Performance                            | . 72 |

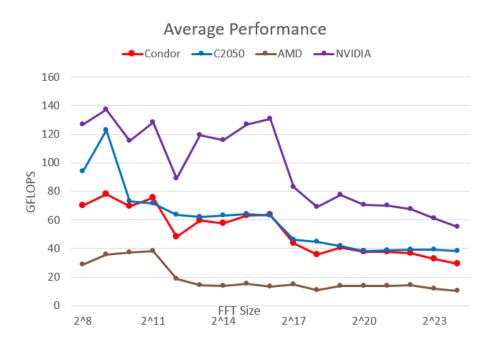

| Figure 32: GPU Cluster Comparison                         | . 73 |

| Figure 33: Shell Script for Execution                     | . 76 |

| Figure 34: Fragment of Windows Batch File                 |      |

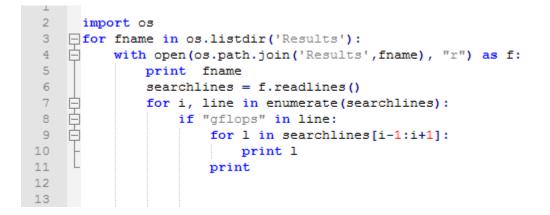

| Figure 35: Python Script for Data Sorting                 | . 78 |

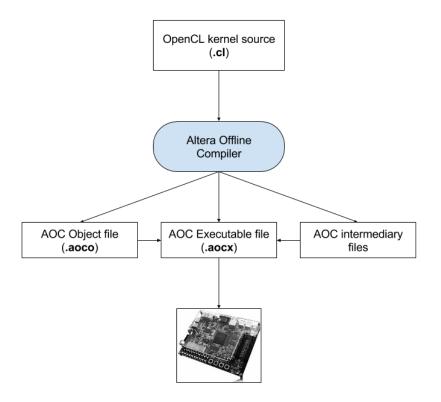

| Figure 36: AOC Flowchart                                  | . 83 |

| Figure 37: Custom Memory Region Targeting                 | . 85 |

| Figure 38: DE1 SoC Development Board                      |      |

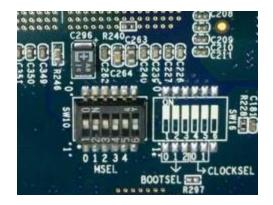

| Figure 39: MSEL Position for Linux with CLI               | . 87 |

| Figure 40: Serial Connection Through PuTTY                | . 88 |

| Figure 41: Contents of init_opencl.sh Script              |      |

|                                                           |      |

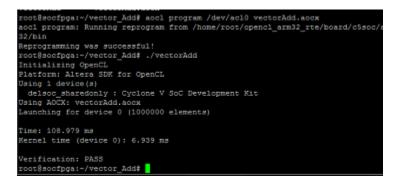

| Figure 42: FPGA Programming and Vector Addition Demo     | 89 |

|----------------------------------------------------------|----|

| Figure 43: Usage Estimation Report for block 64          | 91 |

| Figure 44: Usage Estimation Report for block 16          |    |

| Figure 45: Reference Computation Executed on the ARM CPU |    |

| Figure 46: SoC Power Consumption                         | 94 |

## List of Tables

| Table 1: System Specifications         | . 52 |

|----------------------------------------|------|

| Table 2: CPU Execution System I        | . 54 |

| Table 3: GPU Execution System I        |      |

| Table 4: GPU Execution System II       |      |

| Table 5: CPU Execution System III      |      |

| Table 6: GPU Execution System III      | . 59 |

| Table 7: GPU Speed-up Against Baseline | . 60 |

| Table 8: CPU Execution System IV       |      |

| Table 9: GPU Landscape                 |      |

| Table 10: FPGA Execution Time          |      |

|                                        |      |

8

### **Chapter 1: Introduction**

Generally, the world of computing has accessed two methods of manipulating and interpreting information; firstly, hard-coded designs in the form of ASICs, where data-paths and algorithms are fixed in hardware, resulting in high performance applications that cannot be altered after creation, accomplishing only the task they were designed for. And secondly programmable systems, (meaning CPUs, and more recently GPUs), where algorithms are implemented after production via the use of software, the data path in a programmable system is also fixed, however it implements primitive generics so that it may be used in multiple algorithms, resulting in a higher degree of reusability at the cost of performance. (Altera, 2007)

Fixed implementations like the ASIC are so complex in terms of design and manufacture that the user base for such devices is limited to companies that can afford the time and resource investment. Also with technology moving forward so fast, the overall production time of such a device might end up being longer than the time it takes for new generations of hardware to be created, making ASICs a very niche market. Because of this, the majority of applications use programmable systems based on CPU architecture.

As requirements grow, programmable devices need to improve in order to keep up with the computational demands of users. This is done, generally through three different trends. The first of these trends is the frequency scaling of said systems. However, higher frequencies require higher voltage, making it more difficult to increase frequency without also increasing power consumption. This issue is known as the "power wall" and it refers to the point where increasing frequency would require so much more power that it becomes impractical. (Schaller, 1997)

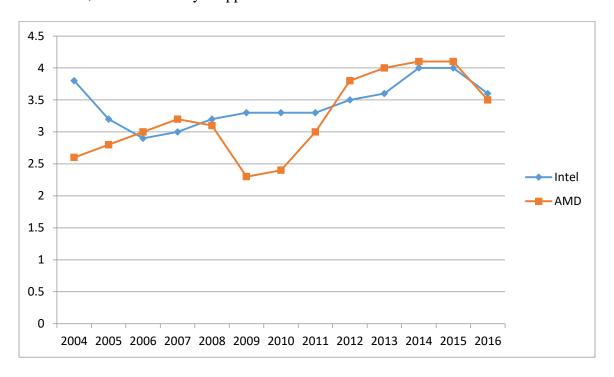

It can be observed in Figure 1 that CPU clock frequency has not seen any major improvements since 2004, and had actually dropped when vendors decided to embrace multi-core architectures.

#### Figure 1: CPU Frequency Evolution (GHz)

A second trend involved reducing the size of transistors in programmable systems, thus increasing the amount of components fitted on the same amount of space. This trend is governed by Moore's Law, an observation stating that the number of transistors in an IC doubles approximately every two years. The observation has stood the test of time since 1975; however the development pace of this trend is also diminishing, with smaller sized transistors taking increasingly more time to develop. Also, this trend is reaching its physical limits, with current technologies offering 14nm chips. The expected end-date of Moore's Law is set for 2025.

| 45 nm<br>icon | 32 nm    | 22 nm    | 14 nm | 10 nm    |

|---------------|----------|----------|-------|----------|

| icon          |          |          |       |          |

|               |          |          |       |          |

| High-k I      | Metal Ga | ate      |       |          |

|               |          | Tri-Gate |       |          |

|               |          |          |       | Tri-Gate |

Figure 2: Intel CPU Architecture Size Evolution (Intel)

Taken together, the above two are closely related in limiting CPU frequency, since cooling capabilities are not scaling at a fast enough rate to allow for the maintaining of high frequencies in more dense systems. This has led to a stagnation, and even decrease, in CPU frequency during the last decade.

The third trend used to improve performance relied on the development of more complex hardware, capable of converting the sequential logic of programming into instruction-level parallelism. Also, because, in software programming, the memory latency of programs is not considered, this task falls on hardware once again, meaning that larger chunks of hardware must be dedicated to managing memory, and extracting parallelism from the code. Over time, the improvements to hardware in programmable systems have seen diminishing returns. (Schaller, 1997)

One attempt to avoid the issues described above was the emergence of Multi-Core processing which involves utilizing more compute units running at slower clock speeds and parallelising the process as to exploit multiple nodes at the same time. To offer an example, the Intel Pentium 570J of 2004 offered a max clock speed of 3.8 GHz and a single core, and the current generation Intel i7-6700k offers a max clock speed of 4.2 GHz with four cores.

Since the benefits of following the three aforementioned trends are diminishing, emphasis is shifted towards creating parallelism at code level instead of relying on hardware to extract it at instruction-level. This means that the developer is tasked with defining parallelism and that the hardware can focus more on the computation and less on interpretation. (Garland & al., 2008)

#### 1.1 Heterogeneous Computing

Any system that uses more than one processor type to handle computational requirement is referred to as a heterogeneous system. The addition of specialized coprocessor to accelerate specific computational tasks as opposed to simply increasing the number of processors is the "definition" of heterogeneous computing. (Kalinov, Lastovetsky, & Robert, 2005)

Heterogeneous systems have found their way into every corner of everyday life, with the CPU-GPU combination being the most common. These are today found in the most so-called "smart" devices, such as phones, tablets or watches. And although devices such as these were not designed with the intent to benefit computing, recent work by the Mont-Blanc project has shown that embedded and mobile devices can be used to power a fully functional supercomputer, with the aim of creating a supercomputing environment that is more energy efficient. (Perez, Bosque, Stafford, & Beivide, 2016)

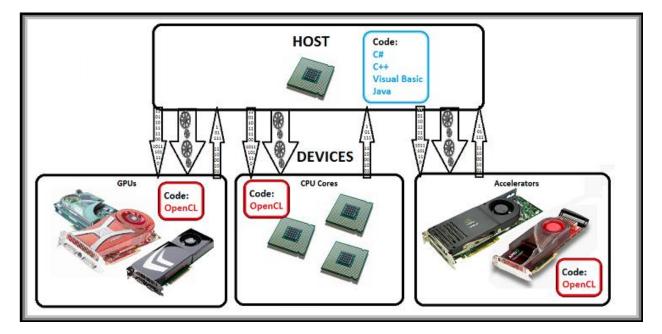

#### **1.2** The OpenCL heterogeneous framework

OpenCL is a development framework that is platform-independent and emphasises parallel computing. This framework is compatible with many platforms, with commercial suppliers such as Intel, NVidia, and AMD all offering support for OpenCL on their hardware.

OpenCL is a programming language derived from ISO C99 that adds API in order to extract parallelism from an otherwise serial programming language. This allows OpenCL to expand the number of applications that can run on an FPGA, and opening it up to a variety of programmers that had no way of using it before. (Stone, Gohara, & Shi, 2010)

Figure 3: Host and Various Accelerators (CMSoft)

The standard use model for OpenCL is split in two parts:

The Host code; a sequential C code written with OpenCL API required to communicate with the chosen platform. This code is compiled into an executable that gets ran on the host CPU, and is responsible for controlling the entire system, from start to finish.

The Kernels; each function ran on the platform is written as a kernel, using OpenCL syntax. This then gets compiled using the SDK offered by the manufacturer of the platform, generating a second executable. The kernel executable is used by the host to programme the platform during run-time.

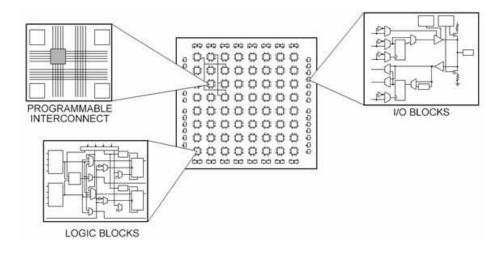

#### 1.3 Reconfigurable Computing

The term reconfigurable computing refers to the act of performing computations via the use of spatially (field) programmable architectures such as FPGAs. This merges a multitude of disciplines, including hardware design, digital signal processing, computer aided design, and sequential and parallel computing. Over the past 25 years, a community dedicated to building and programming these new systems has emerged, and the foundation for large scale reconfigurable computing is being laid.

The FPGA became an attractive solution in the computing world because dedicated hardware was always much faster than its software counterpart. However due to the high design cost and development time of ASIC solutions made it viable only for a select few. Moore's Law also meant that in some cases a faster microprocessor was created before the hard-coded solution meant to outperform it was implemented. FPGAs offered similar hardware specific computational speeds without the development and manufacturing costs or lead times of traditional ASIC solutions. (Tessier, Pocek, & DeHon, 2015)

Figure 4: FPGA Basic Outline (Mazsola)

While the FPGA, through its massive parallel computation capabilities, flexibility, and low energy consumption, provides opportunities for computational acceleration, it also comes with an exponential increase in development time. CPUs and GPUs are programmed using highlevel languages, C and CUDA as an example, which lowers the development time. In contrast, FPGA are programmed in HDL, which in software development terms, is similar to the Assembler language, a low-level language that makes development more time-consuming. FPGA developers also need to take into account hardware design, RTL programming and timing optimisations. This, in turn, requires domain experience for optimal design and implementation.

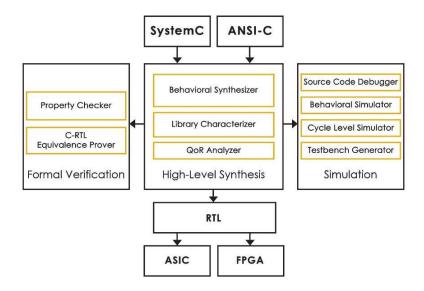

In order to alleviate some of the barriers that prevent FPGA based computing to take root multiple tools have been developed to reduce development time by allowing users to write code in high-level languages, such as C or Java, and having it converted into HDL.

It has been shown that FPGAs offer similar computational power to GPUs in regards to optical flow algorithms, however the development time of such applications is 12 times slower on the FPGA than it is on a GPU. The difference in development time was attributed to the complexity of hardware design and simulation which use the process of "edit/compile/simulate followed by edit/synthesize/place-and-route/execute" as opposed to the software development which requires only an "edit/compile/execute" process. However, taking into account the lower power consumption of the FPGA and its higher affinity to parallelism, it can be assumed that FPGAs have the ability to perform better than GPUs, however the trade-off in development time make it a more situational solution. As such, the introduction of OpenCL development could bring down the development time of such applications. (Bodily, Nelson, Wei, Lee, & Chase, A Comparison Study on Implementing Optical Flow and Digital Communications on FPGAs and GPUs, 2010)

In recent years, interest has changed from using HDL to HLS, standing for High-Level Synthesis, an approach to producing logic circuits that avoids using HDL when possible. This means that HLS tools convert a software based design to a circuit made up of control logic and data path. Parallelism in HLS is achieved through scheduling; multiple instructions are performed during the same clock cycle. This, however, is not the best approach when using FPGAs. These devices benefit a lot from their ability to manage pipelined applications, however current programming languages, like C, are unable to express pipelining and as such, the full potential of the FPGA is not unlocked. Also, HLS is not traditionally used to create an entire system, only small parts of it; this means that the need for a competent HDL developer is not bypassed.

16

Figure 5: C to RTL Converter Using HLS (Aldec)

OpenCL addresses most of the issues posed by HLS by using a host connected to multiple kernels. Each kernel runs independently of the other and the host manages communications. The host part of the system sets up the data to be processed and runs threads on a kernel. Threads are executed by "…reading arguments, loading data from global memory, processing it, and storing the results in global memory." By controlling the OpenCL application through the host file, the designer is able to avoid going into hardware design, removing the need for experience in that domain and allowing for faster development times.

A recent work by Altera Corporation showed that OpenCL based implementations provided comparable if not better results than the HDL-coded alternatives, with much lower development times. This suggests that OpenCL could allow for the development of high-quality computational solutions based on FPGAs much faster than traditional methods. (Altera, 2011) To determine the efficiency of heterogeneous computing, using an OpenCL based programming model, several test-benches will be designed. These will be based on algorithms or compute-heavy tasks that can benefit from the increased native parallelism available in heterogeneous systems. Systems, such as these, would allow for the breakdown of operations between resources in order to maximise performance, for example, assigning serial tasks to CPUs and parallel tasks to GPUs.

These implementations will then be compared with computing solutions offered on the existing systems, which utilise CPU based computation, in order to determine whether heterogeneous computing provides a speed-up factor worthy of consideration. Comparison will not be made solely on runtime speed-up but also on development time, development complexity and power-usage.

An attempt will be made to improve the performance of the High Throughput Computing environment at the University of Huddersfield by taking advantage of the readily available General-Purpose GPUs in the HTCondor pool. This diverse ecosystem spans multiple computer architectures, various operating systems, and a significant variation of compute units, varying from low end CPUs to high-end GPGPUs. Currently, the university exploits the idle CPU time of available machines by assigning them computational tasks, however the GPU resources in these systems are unused. No configuration exists to allow for the allocation of tasks to the GPU component of available computers, and as such their capabilities are wasted during their idle periods. With OpenCL being a platform independent tool, a single implementation is developed to exploit the entire heterogeneous system pool, and HTCondor offers a means to access it. While performance is not inherently sought after in HTC, the ability to accelerate computing without requiring hardware changes, or physical intervention, is still desirable and increases the CPU hours generated by the system. It also enables researchers to use more complex applications that are would normally be too time-consuming when ran on CPUs alone.

A third study will investigate the use of OpenCL for developing FPGA applications aimed at computational applications. The aim is to determine the efficiency of OpenCL design as opposed to traditional HDL design in terms of development time, difficulty of porting applications from CPU to FPGA, and the speed-up obtained when using reconfigurable computing.

#### 1.5 Research Questions:

- Does heterogeneous computing provide enough benefits to warrant a change from traditional systems?

- Is the OpenCL heterogeneous platform mature enough to encourage a shift in development environment used for High-Performance Computing?

- Can FPGAs be used to accelerate computing using the OpenCL platform?

The remainder of this thesis is structured as follows. Chapter II offers insight into the different architectures types that can be exploited for computing purposes, and a review of existing work done in this area. Chapter III introduces the OpenCL platform with a focus on the programming model and usage. Chapter IV covers the implementation of an OpenCL benchmark for use across CPUs and GPUs, with a detailed design process and resulting performance. Chapter V covers the implementation of a different OpenCL benchmark, over a HPC resource composed of hundreds of machines. Chapter VI presents the FPGA related benchmark design and execution, while also discussing the SDK offered by the manufacturer. Chapter VII discusses further research topics in this subject area. Chapter VIII represents the conclusion of this thesis.

### **Chapter 2: Literature Review**

As introduced above, heterogeneous computing refers to the use of multiple types of processors to accelerate the execution of computations within a system. The following pages will detail some of the existing accelerators used in conjunction with CPUs to improve performance.

### 2.1 Many-Core Architectures

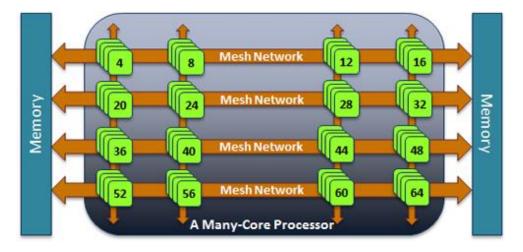

Due to the recent improvements in CPU architectures, the distinct line separating GPUs from CPUs is becoming increasingly blurred. It is due to the emergence of Many-Core architectures that previous boundaries need to be re-evaluated. Many-Core architectures are systems which contain multiple CPU cores within a singular unit, allowing for heavier parallelism at CPU level. This is different from simply connecting multiple CPUs together since it offers much faster memory transfer speeds, and more complex optimisations for parallel execution, at the expense of individual thread performance, and it is in this aspect that Many-Core architectures are similar to GPUs.

Figure 6: Many-Core Processor architecture (Embedded.com)

One such system is the Intel Xeon Phi, a coprocessor unit comprised of up to 72 specialized CPU cores that can be connected to a computer via a PCI-E bus. The Xeon Phi functions, from a programming perspective, as a CPU. It is fully compatible with existing CPU applications that exploit parallelism. The goal of these sorts of architectures is to offer GPU level parallel performance without the inherent drawbacks of GPU based computational design and programming, or the bottlenecks generated by off-chip data transfers. 23 of the top 500 supercomputers are based on the Xeon Phi architecture, including the former number one supercomputer Tianhe-2, the current fastest supercomputer; Sunway TaihuLight also uses many-core processors with 260 cores per unit. (Top500, 2016)

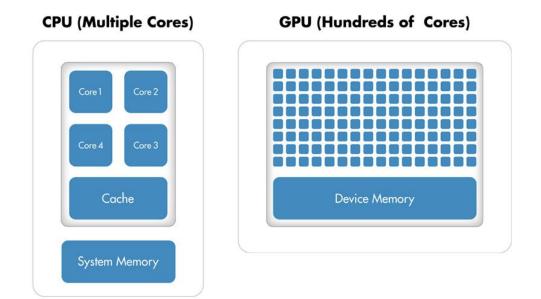

### 2.2 Graphical Processing Units

The Graphical Processing Unit (GPU) is a specialized IC designed for rapid manipulation of data, primarily used in computer graphics and image processing. The GPU, as architecture, contains large amounts of parallel processors, which, while unable to match the frequency of a CPU processor, have demonstrated superiority in tasks that involve parallelism, be it data or task parallelism. However, among the major drawbacks of using GPU accelerators are, the difficulty of programming parallel based applications with fundamentally different approaches to solving, and, on a hardware level, the bottleneck resulting from the need to communicate with a host CPU, that results in abysmal performance when there is limited data to be computed. (Owens, 2008)

A GPU processor is specialized in the sense that it is designed with the following considerations in mind:

22

- 1. Computational requirements are extensive;

- 2. Operations are massively parallel;

- 3. Latency is not as important as throughput;

Figure 7: CPU - GPU Core Count

Constant advances in hardware and programming API's for GPUs have led to an explosion of GPU based computations, with 66 of the top 500 supercomputers being fitted with GPU accelerators. (Top500, 2016)

#### 2.3 Field-Programmable Gate Arrays

These devices present a combination of the hardware efficiency found in hard-coded designs and the re-configurability of programmable systems. Initially developed for replacing multiple transistor-transistor logic devices with a single device, the FPGA was used in connecting a micro-controller to peripherals, interfacing devices, or managing memory banks. It

was designed as a low-cost prototyping solution, and as such was not considered for computational acceleration. Following the fall in transistor costs, and with it the increase in FPGA power, these devices gained ground in the field of verification, rapid prototyping and also low-volume production where ASIC solutions were deemed impractical.

The ever-growing costs of designing and masking ASICs have led to a higher demand for FPGA solutions, increasing, in turn the interest in developing faster and stronger FPGAs. (Altera, 2007)

#### 2.4 Existing Applications

#### 2.4.1 Radar Processing: FPGAs or GPUs?

A white paper by the ALTERA Corporation that discusses the efficiency of FPGA usage in floating-point operations with regards to their usage in radar systems. The reasoning behind this investigation is that CPUs are unable to keep up the pace with current generation processing requirements, and as such are the significant bottleneck in such systems. (Altera, 2013)

The idea of peak FLOP (Floating-Point Operations per Second) as a measure of performance is discussed and dismissed since it represents an indication of the theoretical maximum capability of the device rather than the actual performance in real-world applications. The article then moves on to show that FPGAs are capable of outperforming GPUs when working with small sized algorithms. One given example is the Fast Fourier Transform (FFT), which in radar systems oscillates in length between 512 and 8,192, in general. In this case GPU solutions are ineffective due to overhead and power usage, with FPGAs offering similar computational speeds. The paper stats that GPUs become efficient solutions for FFTs that are

"[...] several hundred thousand points [...]" in length. Based on this, the paper proposes benchmarking solutions based on typical applications.

Following several algorithm based benchmarks, it is concluded that FPGAs can provide lower latency and higher performance than processors; however the advantage of using FPGAs is expected to increase dramatically with the introduction of HPC-optimized FPGAs.

## 2.4.2 A Comparison Study on Implementing Optical Flow and Digital Communications on FPGAs and GPUs

A study made in (2010) set out to determine the performance of both FPGAs and GPUs in signal, and image processing applications. The article studies raw performance as well as design and development effort for both platforms. (Bodily, Nelson, Wei, Lee, & Chase, A comparison study on implementing optical flow and digital communications on FPGAs and GPUs, 2010)

Implementation of the FPGA system was done using a number of readily available IP cores, which limited the system clock rate, and resulted in raw performance approximately 4 times slower than the GPU solution while also having a much higher development effort. The paper also introduces design enhancements for the FPGA that would, in theory, bring the computational performance to values similar to those generated by the GPU.

The study found that while the GPU solution consumed around 200-300W of power, the FPGA consumption bordered on 10W. This allows for FPGAs to be implemented in embedded systems applications where power constraints exist. In terms of speed, the GPU outperformed the

FPGA, however it required large data block sizes to do so, this in term generated large latency issues that aren't encountered in the FPGA implementation.

The development time was approximated to by 12 times higher for the FPGA than the GPU, due to the difficult nature of debugging HDL based applications.

## 2.4.3 Performance Comparison of GPU, DSP and FPGA implementations of image processing and computer vision algorithms in embedded systems

A master's thesis from 2013 studied the implementation of template matching on both FPGAs and GPUs for use in embedded, real-time systems. (Fykse, 2013)

Template matching is a process that requires multiple scans of the same image, for different sizes and orientations of the sought object. For this reason the only viable solutions for real-time applications are GPUs and FPGAs, due to their inherent parallelism.

The author chose to implement the solution from scratch on the FPGA and by using an open-source model for the GPU. Details are given on all steps of the design process, and FPGA testing is done in software, through the use of test-benching, with accuracy determined via comparison with a MATHLAB implementation. For the GPU implementation the OpenCV library is used, allowing for fast and straightforward implementation of the desired system.

When compared, from a development effort stand point, the author debates that even with the use of Intellectual Property and HLS, the FPGA development is a lot more complicated than the GPU one. There is mention of OpenCL as a means of facilitating GPU implementations (however, due to the "age" of the paper, OpenCL is not considered for FPGA implementation). In regards to power consumption, the FPGA far outclasses the GPU, however the FPGA consumption is based on software approximation as hardware testing was not done. Finally, as a pure performance comparison, the GPU performs slightly better than the FPGA at all but the smallest of implementations. The thesis concludes that when faced with real-world projects the higher performance of the GPU must be weighed against the lower power consumption of the FPGA.

#### 2.4.4 Accelerating High-Performance Computing With FPGAs

Published in 2007, this white paper by Altera presents the improvements offered by FPGAs as coprocessors in multiple High-Performance Computing applications. The introduction shows that HPC requirements are increasing at a much faster rate than processors, creating a technology gap. With Moore's Law being outpaced by HPC requirements, the need for specialized coprocessors was introduced. (Altera, 2007)

From a business perspective, higher performance means higher profits (from lower time to market, for example), and as such the need for performance that exceeds Moore's Law is understandable. As processor performance increase is slowing down, and development becomes cost and energy inefficient, application-specific processors are introduced. Ethernet controllers, Graphical processing units and Digital Signal Processors are a few of these solutions; however they are not the answer to the technology gap introduced above, since they only address a single aspect of the problem. The ideal coprocessor is proposed as providing "specific hardware acceleration for key processes within the application", being scalable in performance to keep up with demand and having high-bandwidth, low-latency interfacing to the main processor and system memory.

Apart from these, the paper introduces what it calls the" "four Ps" of HPC market needs: performance, productivity, power, and price." In short, performance refers to the acceleration of the whole system, productivity refers to the ease of configuring the system to run existing software, power refers to the consumption of such systems, which is generally linked to either utilized space or dissipated heat; and finally price, which requires no explanation.

As HPC is shifting away from Massively Parallel Processing toward cluster computing, the coprocessor design needs to be easily integrated into commodity standard architectures "with a cost similar to adding another node in the cluster."

The FPGA is introduced as a solution that satisfies all "four Ps" of HPC needs. Examples are given of FPGA performance increase of standard CPU architectures ranging from 10x to 360x. From a productivity perspective, compilers that convert C to HDL are introduced, thus removing the need for a user to have prior experience with FPGAs in order to use them. For power, the inherent parallelism of FPGAs allow them to greatly reduce operating time compared to sequential systems, resulting in higher performance at slower clocks, in turn resulting in lower power consumption. The final "P", price is also covered by the FPGA which has a cost comparable to a CPU of similar specifications.

## 2.4.5 OpenCL: A Parallel Programming Standard for Heterogeneous Computing Systems

Published in 2010 this work is a very thorough introduction to the OpenCL framework, covering the reasoning behind its development, its predecessors and describing the functionality of the platform. (Stone, Gohara, & Shi, 2010)

The shift toward heterogeneous computing created a need for software development frameworks in the form of parallel programming languages and libraries. Several toolkits were developed targeting multi-core processors and GPUs, namely, OpenMP, CUDA, and others. OpenCL is described as an industry standard for parallel computing targeting heterogeneous systems that, unlike its predecessors, targets a vast majority of hardware devices, and offers a unified environment for development.

The paper describes the OpenCL programming model, device management, development facilitating features of the framework, and memory related aspects of programming. OpenCL is described as targeting architectures that have, up to this point, been poorly supported by vendors in terms of programming tools or libraries. Among the targeted architectures of OpenCL, this work enumerates and expands on multi-core CPUs, GPUs and the IBM Cell processor.

The work offers an in-depth description into the implementation of an application used in bio-molecular science, presenting the different speed-up capabilities of the aforementioned architectures.

#### 2.4.6 A Comprehensive Performance Comparison of CUDA and OpenCL

This 2011 conference paper investigates the performance of both CUDA and OpenCL programming platforms for GPU execution of highly parallel algorithms. This work sets out to determine if using OpenCL sacrifices performance for portability, and if so, identify the trade-offs of using OpenCL as opposed to CUDA. (Fang, Varbanescu, & Sips, 2011)

The work focuses on investigating the performance of CUDA and OpenCL applications for 16 different applications from three different benchmark suites. The tests run initially in this work reveal that CUDA outperforms OpenCL in almost all applications by a margin of up to 30%. However, this is due to the lack of optimizations in the OpenCL applications and the much more mature complier in CUDA.

It is further shown that when developing an application in OpenCL rather than porting it from CUDA, equivalent performance is achieved. OpenCL portability is also investigated with the use of an AMD GPU, an Intel CPU and a Cell/BE accelerator. This revealed that GPU performance remains equivalent when porting but CPUs are limited by the small number of available compute cores and accelerators are not mature enough to support most memory requirements.

The paper proposes the creation of an automated application for optimizing OpenCL applications to different hardware devices and platforms.

### 2.5 Conclusion

It is inferred, based on investigated literature, that no single device, or architecture, is able to outperform the rest in every single aspect of computation, that there is no single fastest device or fastest architecture. These two titles are highly dependent on the task at hand. As such, it is proposed, that rather than being based on a single device, or architecture, a system able to claim the title of fastest computational engine would be comprised of multiple devices and architecture types. It is for this reason that OpenCL, which promises a platform independent framework, for developing applications targeting heterogeneous systems, was selected as the development environment for this work.

31

### **Chapter 3: The OpenCL Platform**

The Open Computing Language framework is a standard that offers a common environment for developing and executing programs on heterogeneous systems, composed of diverse computational devices, such as CPUs, GPUs, FPGAs, and DSPs. OpenCL was initially developed by Apple, together with other large companies like AMD, IBM, NVIDIA, and Intel, which together formed the Khronos Group. The first public release of the OpenCL standard was in 2009 with OpenCL 1. (Stone, Gohara, & Shi, 2010)

OpenCL provides a set of abstractions and programming APIs designed to allow a developer to easily access multiple hardware architectures and devices. The framework defines both a core set of features available to all compliant devices, such as memory management, target device identification, data transfers, or execution queuing, and a more complex extension mechanism that allows device vendors to expose features unique to individual devices, add additional interfaces, or provide device specific optimizations. In doing this, OpenCL allows users to efficiently port applications between different architectures, without losses in features or accuracy.

The framework can be used to exploit heterogeneous systems by allowing a user to match execution segments to the computational hardware architecture most suited to carry them out. It is up to the developer to decide how to divide the application between the various available compute architectures in order to maximize performance.

#### 3.1 Programming Model

Since OpenCL is a platform-independent programming environment, OpenCL based applications will run on compliant system regardless of available hardware. However, it is up the developer to provision the application in such a way that it will execute on multiple device architectures. For example, an application targeting GPU execution will fail to start unless a GPU device is found within the system. As such, the user is expected to design the application with regards to the system it will be executed on. However, this is not the only solution, as the user is also able to design the application with features that allow for device selection, or that prioritize execution on available accelerators. (Stone, Gohara, & Shi, 2010)

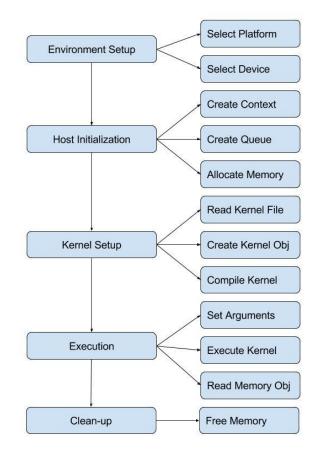

In terms of design, the user is expected to define the targeted computational devices, memory allocations, data management and others within the control segment of the application, namely the host file. The flow of operations during both design and execution can be divided into 5 distinct sections, as evidenced below.

# **OpenCL Programming Flow**

Figure 8: OpenCL Programming Flow

#### 3.1.1 Environment Setup

• Identifying a platform;

A platform is composed of a single host and one or more OpenCL compliant devices. A single computer may have multiple platforms, generally sharing the same host (unless multiple CPUs are available), with each platform being linked to a different OpenCL implementation.

#### • Select device;

The device is the component that will run computation; multiple types can be called (CPUs, GPUs, FPGAs, or other accelerators). With the inherent heterogeneity of OpenCL, a variety of devices may be available at runtime. The application can be designed with a specific architecture in mind, or setup in a way that allows the host to pick which of the available architectures is the fastest.

#### 3.1.2 Host Initialization

• Create Context;

The OpenCL context, created based on selected platform and devices, manages the objects and resources available to the environment, where objects are allocations that enable communication between the host and the compute devices, and allow for management of memory, command queues, objects and execution. A context may contain one or more devices of the same platform.

• Create command queue;

The command queue is the means through which the host sends commands to the device, with each device requiring its own command queue. Commands include device memory allocations, data transfers, kernel executions, and profiling. Commands are queued in the order that they are coded in the program but can be executed out-of-order by flagging them for asynchronous execution.

35

• Create memory objects;

Memory objects are blocks of OpenCL data that can be transferred between host and device. A kernel executing on a device is only able to access data stored within the memory of said device, for this reason the device needs to allocate memory to an object where this data can be stored. Memory allocations can only be created and managed by the host. A memory object, thus, allows the host to access a chuck of memory on the device.

#### 3.1.3 Kernel Setup

• Read kernel file;

The code executed on the computational device is contained as a separate entity, written in a manner that exploits parallelism, using OpenCL specific functions. The host executes this kernel and as such must first read it into memory, and where needed, compile the kernel for device execution. There are multiple ways to pass a kernel file to the host, such as reading it in from an external file or reading in a precompiled binary.

• Create program object;

The program object contains the source or binary for the kernels, a built executable, along with the information required to compile the executable at run time, and the list of devices compatible with the program. Program objects may be created with precompiled kernel binaries or with source codes. Precompiled kernels allow for much faster runtime setup however it limits cross-device compatibility.

#### • Compile kernel;

This optional step creates a binary file for the program object from the source code at runtime, where the precompiled binaries have not been provided within the application, while reducing setup time for execution, this allows an application to target multiple devices without impacting program size or development time.

• Create kernel object;

Based on the program object, a kernel object is instantiated, each containing a kernel function and the argument values used in said function.

## 3.1.4 Execution

• Set kernel arguments;

As the name suggests, this step handles the arguments passed to the kernels, for examples this could be memory size limits, and pointers to the values used in the function. This is done since the host must handle all calls, queues, and executions.

• Execute kernel (Enqueue task);

In order to execute a kernel on the compute device, it needs to be queued in the command queue, and as mentioned before, this can be done either synchronously, in which case commands are executed in order or asynchronously, where commands are executed independently of oneanother. After execution, data from the device memory object must be read back into the host. This can be synchronous (kernel execution is stopped during data transfer) or asynchronous (device keeps computing while data is being transferred).

# 3.1.5 Clean-up

• Free objects;

After all kernels are executed, the host must free the memory objects it has created, or risk crashing the application once device memory has been filled.

## 3.2 On-going Improvements

OpenCL 2.0 has recently introduced major improvements to the standard. As the environment matures, more and more features are added to the APIs. In newer releases of the OpenCL standard, a couple of features stand out due to the improvements they bring to not only the capabilities of the application, but also the reduction of design complexity.

#### **3.2.1 Shared Virtual Memory**

The first of two major improvements brought forth in OpenCL 2.0 is the addition of shared virtual memory. Before its existence, the user had to manage host memory, device memory and communication between the two; this took up a lot of time in design and space in programming. (AMD, 2014)

With the introduction of shared virtual memory, this management is no longer required, there is no need to track buffers and copy information from one point to the other. Shared pointers have been introduced to fix this exact issue.

OpenCL 2.0 introduces two different types of shared memory: Coarse-grain SVM and Fine-grain SVM.

These two types are differentiated by the synchronization points used in updating the buffers, with coarse-grain being updated when the buffers are called, when the kernel is launched, and when it finishes its operation, and fine-grain including the same synchronization points but also at atomic operations. Atomic operations are those operations that are completed in a single time step, relative to other operations, meaning that no other thread can observe an atomic operations execution. The operation is thus indivisible and irreducible, so it can appear to the system as if happening instantaneously.

Coarse-grain only offers a small benefit to programming as it removes the need for individual calls to buffers, but the real improvement can be seen in the (not yet hardware supported) fine-grain SVM, because using this system, buffer mapping/unmapping is no longer required and since buffers update more often, the system can be altered to use data prior to a kernel finishing its main operation.

#### **3.2.2 Device Kernel Enqueue**

With OpenCL 2.0 the device is now able to enqueue kernels, without having to communicate with the host programme. Together with the pipe system, which allows for kernels to exchange data between them, the system will be able to run at much faster speeds, effectively

removing the current bottlenecks constituted by device-host communication speeds. (AMD, 2014)

With kernels given to ability to create new kernels without the use of the host programme, new possibilities arise, where an algorithm can adapt itself without having to transfer data back and forth with the host, limiting device to host communication, one of the main bottlenecks in such a system, to a minimum. One such example is found in networking, where GPUs and FPGAs can be used for much faster network encryption/decryption. The accelerator is able to manage data inputs and outputs, without relying on the host CPU.

## 3.2.3 Standard Portable Intermediate Representation (SPIR-V)

SPIR-V is a standard developed by Khronos, the developers of OpenCL, to facilitate application portability and performance. It is a programming language environment, situated between high-level and low-level languages, which allows for the development of standardized applications for OpenCL drivers. This removes the need to integrate high-level language compilers into device drivers, reducing driver complexity, and improves portability across multiple hardware implementations. (Khronos Group, 2016)

SPIR-V is an attempt to remove the need to precompile binaries for each individual hardware device, leading to a much faster runtime compilation and a smaller development effort.

## 3.3 Conclusion

The use of familiar programming languages and the massive amount of targeted platforms of the OpenCL framework make it a promising solution for developing heterogeneous applications, with a much shorted development cycle and an increased resilience to aging. The ability to easily alter an application so that it targets a different architecture, the ability to increase performance "under-the-hood" via vendor specific optimizations, and the ability to expose features unique to individual devices offer any application developed with the OpenCL framework a much longer lifespan. This also allows for a much faster adoption of newer hardware architectures, without the need to shift to a different development framework, learn a new programming language, and redevelop the application.

# **Chapter 4: OpenCL Multi-Architecture Application Development**

This chapter introduces the utilized test-bench applications developed for testing the efficiency of the OpenCL platform on various workstations containing CPUs and GPUs. The goal was to utilize applications which could operate on different device platforms with minimal changes, and without device specific optimizations, in order to reveal baseline performance, or rather, the worst expected performance of the given systems.

These applications were developed on a Windows based machine using Visual Studio 2013 and the AMD APP SDK version 2.9, chosen based on the specifications of the development machine, although, the choice of development environment did not affect the design of the applications since no device specific optimizations were desired. Applications targeted both the CPU and GPU architecture either in the same package or as separate instantiations of the same application.

In order to test the usability, efficiency and heterogeneity of the OpenCL framework, a benchmarking system was designed based on applications that could exploit the use of massively parallel hardware architectures offered by specialized architectures.

CPU execution was aimed at providing a comparison baseline for all further testing. GPU execution, aimed at both AMD and NVIDIA devices was chosen because the GPU is the most widely available accelerator available. The FPGA was chosen as the second targeted accelerator architecture for OpenCL execution in order to assess both the effectiveness of FPGA based computing for engineering applications and the duration and complexity of OpenCL based designs targeting the FPGA architecture; however this is covered in a separate chapter.

42

## 4.1 OpenCL System Detection

An application was designed to poll the system for compliant OpenCL devices and list their respective features, including core count, clock speed, and maximum memory allocation size. This application lacks OpenCL device specific functionality and thus can report if a system has OpenCL drivers installed or nor and following that what OpenCL devices are identified.

By using this setup it can easily be determined if a system is able to run OpenCL applications or not, and if not, whether the issue is related to available hardware or missing software drivers.

```

// get all platforms

clGetPlatformIDs(0, NULL, &platformCount);

platforms = (cl_platform_id*)malloc(sizeof(cl_platform_id) * platformCount);

clGetPlatformIDs(platformCount, platforms, NULL);

for (i = 0; i < platformCount; i++) {

// get all devices

clGetDeviceIDs(platforms[i], CL_DEVICE_TYPE_ALL, 0, NULL, &deviceCount);

devices = (cl_device_id*)malloc(sizeof(cl_device_id) * deviceCount);

clGetDeviceIDs(platforms[i], CL_DEVICE_TYPE_ALL, deviceCount);

clGetDeviceIDs(platforms[i], CL_DEVICE_TYPE_ALL, deviceCount, devices, NULL);

printf(",");

// for each device print critical attributes

for (j = 0; j < deviceCount; j++) {

</pre>

```

#### Figure 9: Excerpt of Device Detection Application

As see in Figure 9 the application reads all OpenCL platforms, and for each, queries every available device for information. Memory sizes for buffers holding output data are calculated right before data acquisition. This is because the number of platforms and devices is unknown at the design stage and as such pre-allocating memory becomes difficult. The CL\_DEVICE\_TYPE\_ALL parameter ensures that all OpenCL compliant devices are called, and can be altered so that the application only reports CPU, or GPU, or accelerator devices.

```

eport_devices.exe

sting OpenCL Compute Devices:

Device: Turks

OpenCL C version: OpenCL C 1.2

Maximum Clock Frequency: 650 Mhz

Parallel compute units: 6

Intel(R) Core(TM) i5-2320 CPU @ 3.00GHz

C version: OpenCL C 1.2

OpenCl

Maximum Clock Frequency: 2993 Mhz

Parallel compute units:

Intel(R) Core(TM) i5-2320 CPU @ 3.00GHz

evice:

OpenCL C version: OpenCL C

Maximum Clock Frequency: 3000 Mhz

Parallel compute uni

Intel(R) Core(TM) i5-2320 CPU @ 3.00GHz

version: OpenCL C 2.0

OpenCl

Maximum Clock Frequency: 3000 Mhz

Parallel compute units:

```

Figure 10: Device Report for Development PC

The application was designed in two variations, regular and basic output. The regular output reported the most important features of the scanned devices, information that is helpful in determining the performance of the device and certain design parameters, such as maximum workgroup size or memory allocations.

The basic output variation of the application simply returns the device name and compiler version, and is designed to be executed in conjunction with the other applications, to identify the targeted device.

# 4.2 Application Design

This application used a basic, non-optimized matrix multiplication operation using two same-sized matrixes populated with random data at runtime, and reported execution time using OpenCL profiling tools by measuring duration between start of computation until end of data transfer from compute device to host. This is done to account for the communication overhead generated by different workgroup sizes, and delays in transfer caused by slower bus speeds for GPU to CPU communication.

Multiple matrix sizes were employed, ranging from 2<sup>8</sup> up to 2<sup>12</sup>, on multiple workgroup sizes, namely 64, 256, and, where available 1024. The automated allocation of a workgroup size at runtime by the compiler was also utilized, by passing the argument 0 to the workgroup size, allowing the application to determine the best size allocation.

#### 4.2.1 Host Code

The development process began with allocating the memory buffers that will hold the compute elements and resulting data. This is done by determining the size of the matrixes based on the number of elements, as seen in Figure 11. Because the application is designed with square matrixes in mind, number of elements is determined by squaring the number of rows/columns. With the matrix elements being of type float, the necessary memory can easily be determined using the "sizeof" function.

```

//Matrix A memory buffer

unsigned int size_A = pow(matrixsize, 2);

unsigned int mem_size_A = sizeof(float) * size_A;

float* h_A = (float*)malloc(mem_size_A);

//Matrix B memory buffer

unsigned int size_B = pow(matrixsize, 2);

unsigned int mem_size_B = sizeof(float) * size_B;

float* h_B = (float*)malloc(mem_size_B);

```

#### Figure 11: Memory Buffer Allocation

The memory buffers are filled with randomly generated numbers based on a predefined seed making use of C's rand function. Figure 12 illustrates the basic function employed in element allocation.

```

// Allocates a matrix with random float entries.

Devoid randomMemInit(float* data, int size)

{

int i;

for (i = 0; i < size; ++i)

data[i] = rand() / (float)RAND_MAX;

}</pre>

```

#### Figure 12: Function for Matrix Element Allocation

The first step in the aforementioned OpenCL flow is the allocation of a compute platform. In this case, the application allows the user to determine which platform to use for the computation; this is done as a target system may have multiple OpenCL implementations or different compute devices.

```

cl_uint dev_cnt = 0;// initiate platform count

clGetPlatformIDs(0, 0, &dev_cnt);//count platforms

platforms = (cl_platform_id*)malloc(sizeof(cl_platform_id) * dev_cnt);//allocate memory for platform ids

clGetPlatformIDs(dev_cnt, platforms, NULL);//get platform ids

i = 0;//initiate while loop platform count

while (1) {

```

#### Figure 13: Identifying Available Platforms.

As such, the application must first determine how many platforms are available, allocate memory for them, and finally store platform information in memory, as seen in Figure 13. A while loop is created past this that enables a user to pick a targeted platform based on the compute devices existing within the platform, Figure 14. The user is then asked to pick between targeting a CPU device on the platform or a GPU device, Figure 15.

Note: The application is not optimized to work with platforms that contain multiple devices of the same type and will always pick the first one detected.

```

// for each device print device name

for (j = 0; j < deviceCount; j++) {

clGetDeviceInfo(devices[j], CL_DEVICE_NAME, 0, NULL, &valueSize);

value = (char*)malloc(valueSize);

clGetDeviceInfo(devices[j], CL_DEVICE_NAME, valueSize, value, NULL);

printf("Device name is %s \n\n", value);

free(value);

}

printf("Do you want to use this platform ? (y/n)\n");// ask for platform</pre>

```

Figure 14: Device Cycle Loop

```

printf("Do you want to use a GPU ? (y/n)\n");// ask for platform

cond = "";

cond = getchar();

while (getchar() != '\n');

if (cond == 'y')

{

// Connect to a compute device

err = clGetDeviceIDs(platforms[i], CL_DEVICE_TYPE_GPU, 1, &device_id, NULL);

if (err != CL_SUCCESS)

{

printf("Error: Failed to create a device group!\n");

return EXIT FAILURE;

}

}

else

{

err = clGetDeviceIDs(platforms[i], CL_DEVICE_TYPE_CPU, 1, &device_id, NULL);

if (err != CL_SUCCESS)

{

printf("Error: Failed to create a device group!\n");

return EXIT_FAILURE;

}

}

```

Figure 15: CPU/GPU Decision Point

Once user input has been finished the application creates the OpenCL context based on the chosen device's ID. It can be noted in Figure 15 that each is called with error checking in place. The command queue is initiated, with OpenCL profiling enabled, in order to determine total execution time of kernels, Figure 16.

```

// Create a command commands

commands = clCreateCommandQueue(context, device_id, CL_QUEUE_PROFILING_ENABLE, &err);

if (!commands)

{

printf("Error: Failed to create a command commands!\n");

return EXIT_FAILURE;

}

```

Figure 16: Command Queue Initialization

The OpenCL kernel is loaded from a separate file that is read into memory during

runtime and then compiled into an executable based on the chosen architecture. This allows for

device portability however it does not affect profiling times, Figure 17.

```

program = clCreateProgramWithSource(context, 1, (const char **)& KernelSource, NULL, &err);

if (!program)

{

printf("Error: Failed to create compute program!\n");

return EXIT_FAILURE;

}

// Build the program executable

err = clBuildProgram(program, 0, NULL, NULL, NULL, NULL);

if (err != CL_SUCCESS)

{

```

Figure 17: Building Program Executable

Once the compute kernel is creates, memory must be allocated on the device to contain all three matrixes, the first two are copied from the host, and the first is merely instantiated, as it will contain the result of the matrix multiplication, Figure 18.

```

// Create the input and output arrays in device memory for our calculation

d_A = clCreateBuffer(context, CL_MEM_READ_WRITE | CL_MEM_COPY_HOST_PTR, mem_size_A, h_A, &err);

d_B = clCreateBuffer(context, CL_MEM_READ_WRITE | CL_MEM_COPY_HOST_PTR, mem_size_B, h_B, &err);

d_C = clCreateBuffer(context, CL_MEM_READ_WRITE, mem_size_A, NULL, &err);

```

Figure 18: Allocating Device Memory

The kernel arguments are then passed; they contain the memory buffers and matrix sizes,

48

Figure 19

```

err = clSetKernelArg(kernel, 0, sizeof(cl_mem), (void *)&d_C);

err |= clSetKernelArg(kernel, 1, sizeof(cl_mem), (void *)&d_A);

err |= clSetKernelArg(kernel, 2, sizeof(cl_mem), (void *)&d_B);

err |= clSetKernelArg(kernel, 3, sizeof(int), (void *)&matrixsize);

err |= clSetKernelArg(kernel, 4, sizeof(int), (void *)&matrixsize);

if (err != CL_SUCCESS)

{

printf("Error: Failed to set kernel arguments! %d\n", err);

exit(1);

}

```

Figure 19: Kernel Argument Passing

At this stage, Work-group and Work-item sizes are set and the kernel is queued in the

command queue for execution, and the application waits for the kernel cu finish, Figure 20.

```

localWorkSize[0] = worgroupsize;

localWorkSize[1] = worgroupsize;

globalWorkSize[0] = size_m;

globalWorkSize[1] = size_m;

err = clEnqueueNDRangeKernel(commands, kernel, 2, NULL, globalWorkSize, localWorkSize, 0, NULL, &event);

if (err != CL_SUCCESS)

{

printf("Error: Failed to execute kernel! %d\n", err);

exit(1);

}

clWaitForEvents(1, &event);

```

Figure 20: Command Enqueue

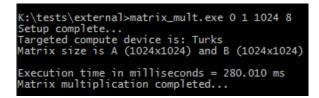

Finally, the contents of the calculated matrix memory buffer are read back into the host and profiling data is called in order to determine execution duration. This duration is calculated using built-in profiling tools offered by the OpenCL framework, and take into account the duration between the first and last command executed by the kernel on the compute device, Figure 21.

```

err = clEnqueuReadBuffer(commands, d_C, CL_TRUE, 0, mem_size_C, h_C, 0, NULL, NULL);

if (err != CL_SUCCESS)

{

printf("Error: Failed to read output array! %d\n", err);

exit(1);

}

clGetEventProfilingInfo(event, CL_PROFILING_COMMAND_START, sizeof(time_start), &time_start, NULL);

clGetEventProfilingInfo(event, CL_PROFILING_COMMAND_END, sizeof(time_end), &time_end, NULL);

total_time = time_end - time_start;

printf("\nExecution time in milliseconds = %0.3f ms\n", (total_time / 1000000.0));

printf("Matrix multiplication completed...\n");

```

Figure 21: Data Retrieval and Profiling

Last but not least, all memory allocations are cleared and the application terminates,

Figure 22.

```

//Memory clearing

free(h_A);

free(h_B);

free(h_C);

clReleaseMemObject(d_A);

clReleaseMemObject(d_C);

clReleaseMemObject(d_B);

clReleaseProgram(program);

clReleaseKernel(kernel);

clReleaseCommandQueue(commands);

clReleaseContext(context);

```

Figure 22: Memory Clearing

### 4.2.2 Kernel Code

The kernel code is fairly straightforward, it takes in the global buffers containing the two populated matrixes, the buffer containing the output matrix and the number of rows and columns of the matrixes. It defines the two working dimensions using a work-item ID call, "get\_global\_id", and based on this information calculated the value of each individual element of the resulting matrix, Figure 23.

50

```

<u>___kernel void</u>

matrixMul(__global float* C,

__global float* A,

__global float* B,

int wA, int wB)

{

int tx = get_global_id(0);

int ty = get_global_id(1);

float value = 0;

for (int k = 0; k < wA; ++k)

{

float elementA = A[ty * wA + k];

float elementB = B[k * wB + tx];

value += elementA * elementB;

}

C[ty * wA + tx] = value;

}

```

Figure 23: OpenCL Kernel Code

Later versions of the application used external arguments as opposed to user input in order to facilitate batch execution. The information passed externally was, platform number, device type, matrix size and workgroup size, Figure 24.

51

```

∃int main(int argc, char** argv)

{

unsigned int matrixsize = size m;

unsigned int WGsize = worgroupsize;

unsigned int arctype = 1;

unsigned int plat = 0;

// External Arguments

if (argc == 5)

{

plat = atoi(argv[1]);

arctype = atoi(argv[2]);

matrixsize = atoi(argv[3]);

WGsize = atoi(argv[4]);

}

else

{

printf("\n\nError: Insuficient Arguments Passed \n");

printf("Please provide:\n");

printf("1. Platform Number( Start at 0)\n");